# Bi-Directional GaNFast™

### 1. Features

- Bi-Directional 4-Quadrant GaN power switch:

- Vss 650V continuous / 800V transient

- + 102m  $\Omega$  Rss(on)\_typ\_25c and 25A Iss(cont\_25c)

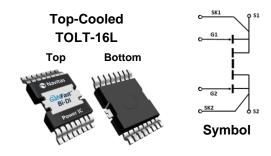

- TOLT-16L thermally-enhanced, top-cooled

- Zero reverse-recovery charge

- Up to 2MHz operation

- GaNFast<sup>™</sup> technology:

- Integrated active substrate clamp circuit between each source and the common substrate, optimizing switching performance in bi-directional current flow

- RoHS, Pb-free, REACH-compliant

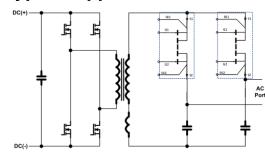

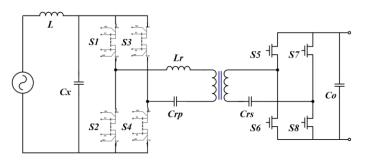

## 2. Applications / Topologies

- Solar Micro-inverter / ESS and Heric Inverter

- Bi-Directional ZVS Cyclo-converter topologies

- AC-AC Motor Drive and Matrix Converters

- Next-generation Bi-Directional topologies

4. Typical Application Circuits

### 3. Description

NV6427 is an **optimized** bi-directional switch capable of blocking voltage in both directions. A monolithic, integrated substrate clamping circuit between each source and the common substrate automatically clamps source-to-substrate voltage. Navitas' unique substrate clamp technology allows optimized switching performance during 4quadrant operation versus a **floating substrate** switch which can suffer 'back-gating effect'.

NV6427 also implements a thermally-enhanced top-cooled SMD with gull wing leads for superior board level temp cycling.

NV6427 is the ideal choice for topologies utilizing 4-quadrant switches to capture the benefits of bidirectional GaN for high-frequency, high-powerdensity, high-efficiency systems in solar, industrial, motor drive, and EV segments.

Cycloconverter

**Ultra-High Power Density Onboard Charger**

DATASHEET

### 5. Table of Contents

| (1) <u>Features</u>                      | pg. 1     |

|------------------------------------------|-----------|

| (2) Applications / Topologies            | pg. 1     |

| (3) Description                          | pg. 1     |

| (4) Typical Application Circuits         | pg. 1     |

| (5) <u>Table of Contents</u>             | pg. 2     |

| (6)Nomenclature Definitions              | pg. 3     |

| (7) Absolute Maximum Ratings             | pg. 4     |

| (8) Recommended Operating Conditions     | pg. 4     |

| (9) <u>ESD Ratings</u>                   | pg. 4     |

| (10) Thermal Resistance                  | pg. 4     |

| (11) Electrical Characteristics          | pg. 5~6   |

| (12) Inductive Switching Circuit Diagram | pg. 7     |

| (13) <u>Electrical Curves</u>            | pg. 8~11  |

| (14) <u>Pinout Table</u>                 | pg. 12    |

| (15) Functional Description              | pg. 13~16 |

| (15.1) <u>4QS Operating Modes</u>        | pg. 13    |

| (15.2) Integrated Substrate Clamp        | pg. 14    |

| (15.3) Isolated Driver Selection         | pg. 14    |

| (15.4) PCB Layout Guidelines             | pg. 15    |

| (16) Package Outline Dimensions          | pg. 16    |

| (17) <u>TnR Drawing</u>                  | pg. 17    |

| (18) Ordering Information                | pg. 18    |

| (19) <u>Revision History</u>             | pg. 18    |

### 6. Nomenclature

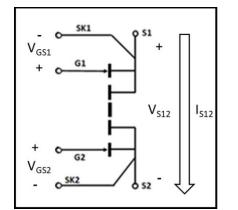

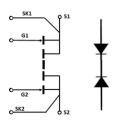

Fig. 1.  $V_{GS1}$ ,  $V_{GS2}$ ,  $V_{S12}$ ,  $I_{S12}$  Definition (Note 1 - 3)

**NV64**

DATASHEE

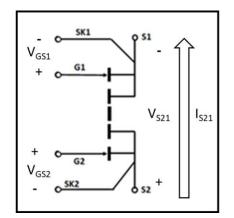

Fig. 2.  $V_{GS1}$ ,  $V_{GS2}$ ,  $V_{S21}$ ,  $I_{S21}$  Definition (Note 1 - 3)

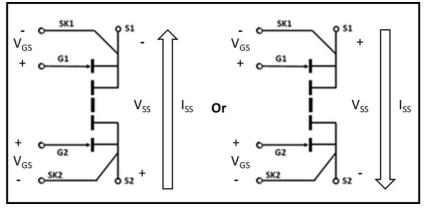

Fig. 3. V<sub>GS</sub>, V<sub>SS</sub>, I<sub>SS</sub> Definition (Note 4 - 6)

- (1) V<sub>GS1</sub> implies that voltage is measured from gate\_1 to source\_1.

- (2)  $V_{S12}$  implies that voltage is measured from source\_1 to source\_2.

- (3)  $I_{S12}$  implies that current is flowing from source\_1 to source\_2.

- (4)  $V_{GS}$  implies that  $V_{GS} = V_{GS1} = V_{GS2}$ .

- (5)  $V_{SS}$  implies that the source-to-source voltage can be applied in either direction.

- (6)  $I_{SS}$  implies that the source-to-source current can flow in either direction.

- (7) The device is symmetric. All measurements listed with respect to gate\_1 or source\_1 are the same when measured with respect to gate\_2 or source\_2.

### 7. Absolute Maximum Ratings (Note 8) (with respect to source, T<sub>CASE</sub> = 25°C, unless specified)

| Symbol                  | Parameter                                                                                                                       | Мах          | Units |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------|-------|

| V <sub>SS_(CONT)</sub>  | Continuous Source-to-Source Voltage                                                                                             | -650 to +650 | V     |

| V <sub>SS_(TRAN)</sub>  | Transient Source-to-Source Voltage (Note 9)                                                                                     | -800 to +800 | V     |

| V <sub>GS</sub>         | Continuous Gate-to-Source Voltage                                                                                               | -10 to +7    | V     |

| Vgs_(tran)              | Transient Gate-to-Source Voltage                                                                                                | -20 to +10   | V     |

| I <sub>SS_(CONT)</sub>  | Continuous Current ( $T_{CASE} = 25^{\circ}C$ )<br>Continuous Current ( $T_{CASE} = 100^{\circ}C$ , $T_{JUNC} = 150^{\circ}C$ ) | 25<br>16     | А     |

| I <sub>SS_(PULSE)</sub> | Pulsed Current (10μs @ T <sub>JUNC</sub> = 25°C)<br>Pulsed Current (10μs @ T <sub>JUNC</sub> = 150°C)                           | 39<br>16     | А     |

| dV/dt                   | Source-to-Source Slew Rate                                                                                                      | 30           | V/ns  |

| T <sub>JUNC</sub>       | Operating Junction Temperature                                                                                                  | -40 to +150  | °C    |

| T <sub>STOR</sub>       | Storage Temperature                                                                                                             | -55 to +150  | °C    |

(8) Absolute maximum ratings are stress ratings, and subjecting devices to stresses beyond these ratings may cause permanent damage.

(9)  $V_{SS (TRAN)}$  allows for surge ratings during *non-repetitive* events that are < 100 µs.

### 8. Recommended Operating Conditions (Note 10)

fy Our World™

| Symbol          | Parameter          | Min | Тур | Max | Units |

|-----------------|--------------------|-----|-----|-----|-------|

| V <sub>GS</sub> | Gate Drive Voltage |     |     | 6.5 | V     |

(10) Exposure to conditions beyond maximum recommended operating conditions for extended periods of time may affect device reliability.

### 9. ESD Ratings

| ſ | Symbol | Parameter                              | Мах | Units |  |

|---|--------|----------------------------------------|-----|-------|--|

|   | CDM    | Charged Device Model (per JS-002-2014) | 750 | V     |  |

### **10. Thermal Resistance**

| Symbol                             | Parameter                           | Тур | Units |

|------------------------------------|-------------------------------------|-----|-------|

| $R_{_{\Theta_{JUNC}\text{-}CASE}}$ | Junction-to-Case Thermal Resistance |     | °C/W  |

Electrify Our World™

Conditions unless specified:  $V_{ss} = 400V$ ,  $V_{cs} = 6.5V$ ,  $T_{case} = 25^{\circ}C$ ,  $I_{ss} = 6A$

| Symbol                                                                    | Parameter                                          | Min | Тур  | Max | Units | Conditions                                                                 |  |  |

|---------------------------------------------------------------------------|----------------------------------------------------|-----|------|-----|-------|----------------------------------------------------------------------------|--|--|

| 4-Quadrant GaN Switch Characteristics                                     |                                                    |     |      |     |       |                                                                            |  |  |

| I <sub>SSS</sub>                                                          | Source-Source Leakage Current                      |     | 75   |     | μA    | V <sub>SS</sub> = 650V, V <sub>GS</sub> = 0V                               |  |  |

| I <sub>sss</sub>                                                          | Source-Source Leakage Current                      |     | 70   |     | μA    | $V_{SS} = 650V, V_{GS} = 0V,$<br>Tjunc = 150°C                             |  |  |

| I <sub>GSS</sub>                                                          | Gate-Source Leakage Current                        |     | 45   |     | μA    | V <sub>GS</sub> = 6.5V                                                     |  |  |

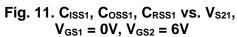

| $R_{SS(ON)}$                                                              | Source-Source Resistance                           |     | 102  | 140 | mΩ    | V <sub>GS</sub> = 6.5V, I <sub>SS</sub> = 6A                               |  |  |

| R <sub>SS(ON)</sub>                                                       | Source-Source Resistance                           |     | 245  |     | mΩ    | $V_{GS} = 6.5V$ , $I_{SS} = 6A$ ,<br>$T_{JUNC} = 150^{\circ}C$ (by Design) |  |  |

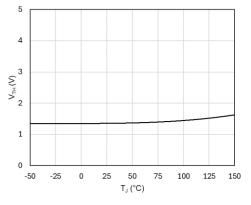

| $V_{GS1(th)}$                                                             | Gate Threshold Voltage                             | 1   | 1.5  | 2.8 | V     | Is21 = 11.5mA, Vs21 = 0.1V                                                 |  |  |

| V <sub>S12_Reverse</sub>                                                  | Source-Source Third Quadrant<br>Conduction Voltage |     | 3.3  |     | V     | $V_{GS1} = 0V, V_{GS2} = 6.5V, I_{S12} = 6A$                               |  |  |

| $Q_{_{\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | Reverse Recovery Charge                            |     | Zero |     | nC    |                                                                            |  |  |

| R <sub>G</sub>                                                            | Internal Gate Resistance                           |     | 700  |     | mΩ    | By Design                                                                  |  |  |

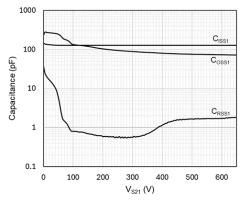

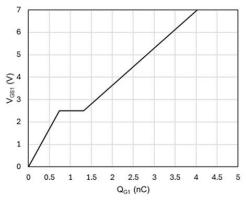

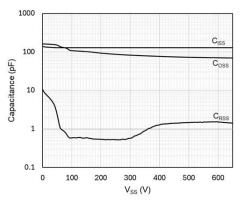

| C <sub>ISS</sub>                                                          | Input Capacitance                                  |     | 128  |     | pF    | V <sub>SS</sub> = 400V, V <sub>GS</sub> = 0V                               |  |  |

| C <sub>ISS1</sub>                                                         | Input Capacitance                                  |     | 128  |     | pF    | $V_{S21} = 400V, V_{GS1} = 0V, V_{GS2} = 6.5V$                             |  |  |

| C <sub>oss</sub>                                                          | Output Capacitance                                 |     | 77   |     | pF    | V <sub>SS</sub> = 400V, V <sub>GS</sub> = 0V                               |  |  |

| C <sub>OSS1</sub>                                                         | Output Capacitance                                 |     | 81   |     | pF    | $V_{S21} = 400V, V_{GS1} = 0V,$<br>$V_{GS2} = 6.5V$                        |  |  |

| Crss                                                                      | Reverse Transfer Capacitance                       |     | 1.29 |     | pF    | V <sub>SS</sub> = 400V, V <sub>GS</sub> = 0V                               |  |  |

| C <sub>RSS1</sub>                                                         | Reverse Transfer Capacitance                       |     | 1.16 |     | pF    | V <sub>S21</sub> = 400V, V <sub>GS1</sub> = 0V,<br>V <sub>GS2</sub> = 6.5V |  |  |

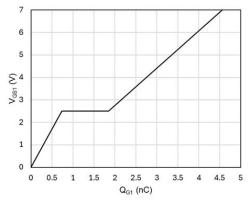

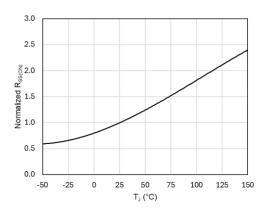

| Q <sub>G</sub>                                                            | Total Gate Charge for Each Gate                    |     | 3.08 |     | nC    | $V_{S21} = 400V, V_{GS1} = 0V \text{ to } 6.5V, V_{GS2} = 0V$              |  |  |

| Q <sub>G1</sub>                                                           | Total Gate Charge for Each Gate                    |     | 3.62 |     | nC    | $V_{S21} = 400V, V_{GS1} = 0V \text{ to } 6.5V, V_{GS2} = 6.5V$            |  |  |

| Q <sub>GS</sub>                                                           | Gate-Source Charge for Each<br>Individual Gate     |     | 0.74 |     | nC    | $V_{S21} = 400V, V_{GS1} = 0V \text{ to } 6.5V,$<br>$V_{GS2} = 0V$         |  |  |

| Q <sub>GS1</sub>                                                          | Gate-Source Charge for Each<br>Individual Gate     |     | 0.74 |     | nC    | $V_{S21} = 400V, V_{GS1} = 0V \text{ to } 6.5V, V_{GS2} = 6.5V$            |  |  |

NV6427

DATASHEET

|                               | Navitas                                         | Bi-Directional Ĝ | àNFast | MV6427<br>DATASHEET                                 |

|-------------------------------|-------------------------------------------------|------------------|--------|-----------------------------------------------------|

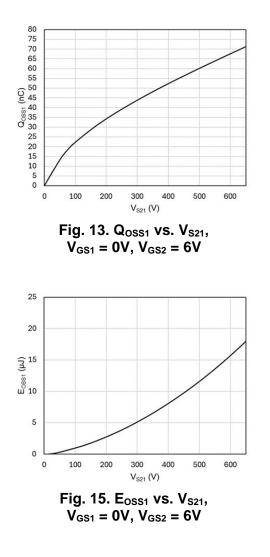

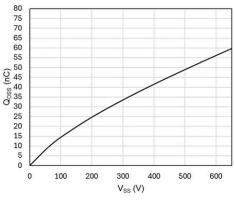

| Q <sub>oss</sub>              | Output Charge                                   | 42               | nC     | V <sub>SS</sub> = 400V, V <sub>GS</sub> = 0V        |

| Q <sub>OSS1</sub>             | Output Charge                                   | 52               | nC     | $V_{S21} = 400V, V_{GS1} = 0V,$<br>$V_{GS2} = 6.5V$ |

| C <sub>O(er)</sub> (Note 11)  | Effective Output Capacitance,<br>Energy Related | 90               | pF     | V <sub>SS</sub> = 400V, V <sub>GS</sub> = 0V        |

| C <sub>O(er)1</sub> (Note 12) | Effective Output Capacitance,<br>Energy Related | 101              | pF     | $V_{S21} = 400V, V_{GS1} = 0V,$<br>$V_{GS2} = 6.5V$ |

| C <sub>O(tr)</sub> (Note 13)  | Effective Output Capacitance,<br>Time Related   | 105              | pF     | V <sub>SS</sub> = 400V, V <sub>GS</sub> = 0V        |

| C <sub>O(tr)1</sub> (Note 14) | Effective Output Capacitance,<br>Time Related   | 131              | pF     | $V_{S21} = 400V, V_{GS1} = 0V,$<br>$V_{GS2} = 6.5V$ |

(11)  $C_{O(er)}$  is a fixed capacitance that gives the same stored energy as  $C_{OSS}$  while  $V_{SS}$  rises from 0V to 400V.

(12)  $C_{O(er)1}$  is a fixed capacitance that gives the same stored energy as  $C_{OSS1}$  while  $V_{SS}$  rises from 0V to 400V.

(13)  $C_{O(tr)}$  is a fixed capacitance that gives the same charging time as  $C_{OSS}$  while  $V_{SS}$  rises from 0V to 400V.

(14)  $C_{O(tr)1}$  is a fixed capacitance that gives the same charging time as  $C_{OSS1}$  while  $V_{SS}$  rises from 0V to 400V.

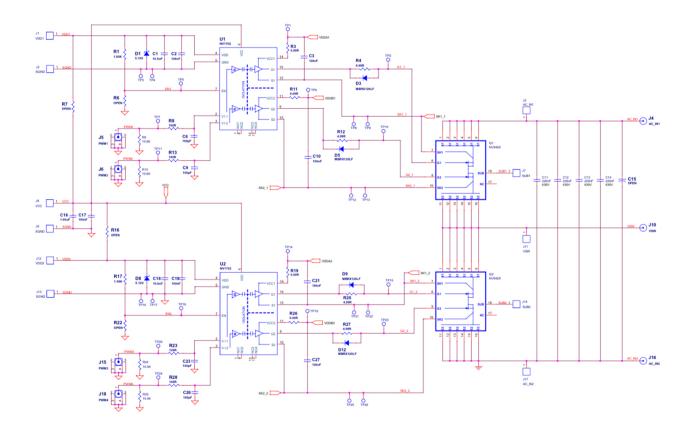

## 12. Inductive Switching Test Circuit

Schematic 1. Inductive Switching Test Circuit

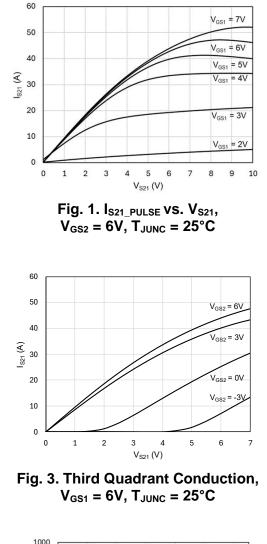

### 13. Electrical Curves (GaN FET, T<sub>CASE</sub> = 25°C unless otherwise specified)

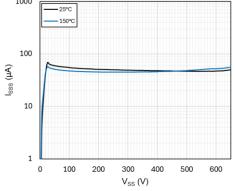

Fig. 5. I<sub>SSS</sub> vs. V<sub>SS</sub>, T<sub>JUNC</sub> = 25°C, 150°C

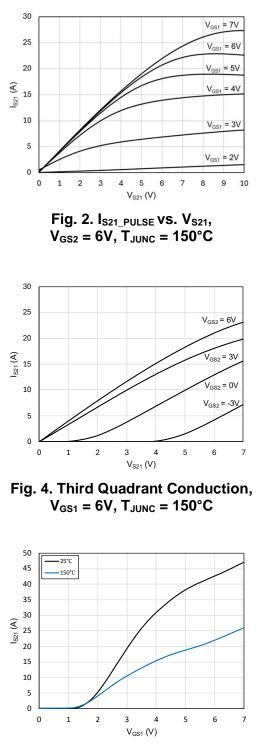

Fig. 6.  $I_{S21_PULSE}$  vs.  $V_{GS1}$ ,  $V_{GS2} = 6V$ ,  $V_{S21} = 10V$

8

# vitas Bi-Directional ĜaNFast NV642

# 7 DATASHEET

Electrify Our World

Fig. 7. V<sub>GS(th)</sub> vs. T<sub>JUNC</sub>

Fig. 9.  $V_{GS1}$  vs.  $Q_{G1}$ ,  $V_{GS2} = 6V$

Fig. 8. Normalized R<sub>SS(ON)</sub> vs. T<sub>JUNC</sub>

Fig. 10.  $V_{GS1}$  vs.  $Q_{G1}$ ,  $V_{GS2} = 0V$

Fig. 12.  $C_{ISS}$ ,  $C_{OSS}$ ,  $C_{RSS}$  vs.  $V_{SS}$ ,  $V_{GS} = 0V$

# vitas **Electrify Our World**

# Bi-Directional GaNFast NV6427

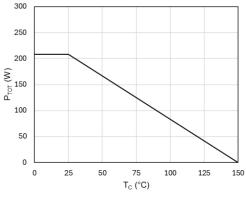

Fig. 17. PDISSIPATION VS. TCASE

Fig. 14.  $Q_{OSS}$  vs.  $V_{SS}$ ,  $V_{GS} = 0V$

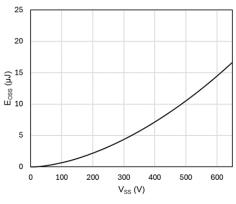

Fig. 16.  $E_{OSS}$  vs.  $V_{SS}$ ,  $V_{GS} = 0V$

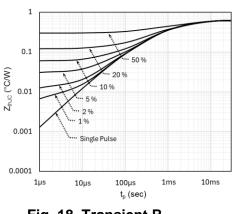

Fig. 18. Transient ROJUNC-CASE

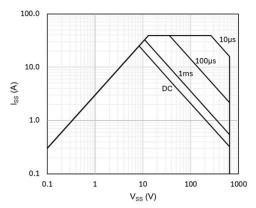

Fig. 19. Safe Operating Area, T<sub>JUNC</sub> = 25°C

DATASHEET

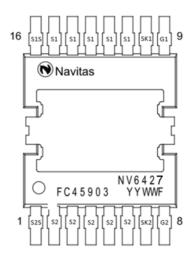

## 14. Pinout Table

| Pin     |                                        | 1/0                                         | Description          |  |

|---------|----------------------------------------|---------------------------------------------|----------------------|--|

| Number  | Symbol                                 | 1/0                                         | Description          |  |

| 1       | S2S                                    | Р                                           | Connect to S2 on PCB |  |

| 2-6     | S2                                     | Р                                           | Source 2 Terminal    |  |

| 7       | SK2                                    | G                                           | Kelvin Source 2      |  |

| 8       | G2                                     | Ι                                           | Gate 2               |  |

| 9       | G1                                     | Ι                                           | Gate 1               |  |

| 10      | SK1                                    | G                                           | Kelvin Source 1      |  |

| 11-15   | S1                                     | Р                                           | Source 1 Terminal    |  |

| 16      | S1S                                    | Р                                           | Connect to S1 on PCB |  |

| Top Pad | N/A                                    | N/A Substrate: Requires Isolation to Heatsi |                      |  |

|         | Note: I = Input, P = Power, G = Ground |                                             |                      |  |

# 15. Functional Description

avitas

Electrify Our World

#### 15.1. Operating Modes

NV6427 is a normally-off GaNFET device with two gates (G1, G2) and two sources (S1, S2). G1 acts with respect to S1, and G2 acts with respect to S2, but G2 does not act with respect to S1, and vice-versa. As a 4-Quadrant Switch (4QS), it is capable of blocking voltage in either or both directions, and conducting current in either or both directions, depending on the states of G1 and G2.

Bi-Directional Ĝȧ̀NFast™

**Mode 1** ( $V_{GS1} = 0V$ ,  $V_{GS2} = 0V$ ): Voltage is blocked in both the  $V_{S12}$  and  $V_{S21}$  direction. Current is blocked in both the  $I_{S12}$  and  $I_{S21}$  direction.

**Mode 2** ( $V_{GS1} = 6.5V$ ,  $V_{GS2} = 0V$ ): Voltage is blocked in the  $V_{S12}$  direction only. Current flows in the  $I_{S21}$  direction but is blocked in the  $I_{S12}$  direction.  $V_{S21}$  should not exceed 7V.

**Mode 3** ( $V_{GS1} = 0V$ ,  $V_{GS2} = 6.5V$ ): Voltage is blocked in the  $V_{S21}$  direction only. Current flows in the  $I_{S12}$  direction but is blocked in the  $I_{S21}$  direction.  $V_{S12}$  should not exceed 7V.

**Mode 4** ( $V_{GS1} = 6.5V$ ,  $V_{GS2} = 6.5V$ ): Current can flow in either direction. If  $V_{S12} > V_{S21}$ , then current flows in the  $I_{S12}$  direction. If  $V_{S21} > V_{S12}$ , then current flows in the  $I_{S21}$  direction.

Datasheet

**NV64**

DATASHEE

### 15.2. Integrated Substrate Clamp

NV6427 has a monolithic, integrated substrate clamping circuit which optimizes the silicon substrate potential under any bias condition applied between the two sources. This clamp circuit prevents undesired  $R_{SS(ON)}$  increases that can happen when the silicon substrate potential is uncontrolled.

This major performance enhancement is possible by virtue of Navitas *GaNFast*<sup>™</sup> technology and this functionality differentiates NV6427 from competitor parts.

### 15.3. Gate Driver and Gate Power Supply Selection

NV6427 Bi-Directional Switch requires two floating gate driver channels to provide PWM-generated gate drive inputs to the two gates. An isolated driver is recommended, providing 6V~6.5V output voltage for best performance and should be able to turn on both gate outputs simultaneously (Mode 4 operation). The type of isolation is dependent on the circuit and system requirements. Functional isolation may be enough in many cases, but in some cases safety isolation may also be needed.

At least one of the two gates will not be referenced to ground or a DC rail and will require a drive channel that can float to high voltage that matches the range of the source it is driving. In some applications, both sources are switching nodes, so both gate drive outputs and the power supplies for them must be able to float to remain referenced to the source being driven. In some circuits, a ground referenced power supply and a bootstrap power supply is sufficient, while in others an isolated floating power supply for one or both gate drives may be required.

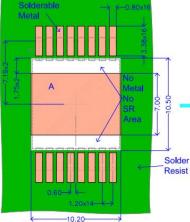

### 15.4. PCB Layout Guidelines and PCBA SMT Guidelines

PCB layout is critical for thermal management, noise immunity, and proper operation of the device. The following rules should be followed carefully during the design of the PCB layout:

• Do not run power SOURCE current through SK pin!

### PCBA SMT Guidelines:

- 1.6mm thick FR4, 4-Layer 2-Oz Cu

- Solder Mask per DWG on left

- Solder Stencil per Customer's PCBA SMT

- Solder Reflow Profile per PCBA SMT Vendor

- Recommended Solder Paste: SAC305

- Recommended 10% maximum Voids

RECOMMENDED PCB FOOTPRINT

RECOMMENDED STENCIL OPENING

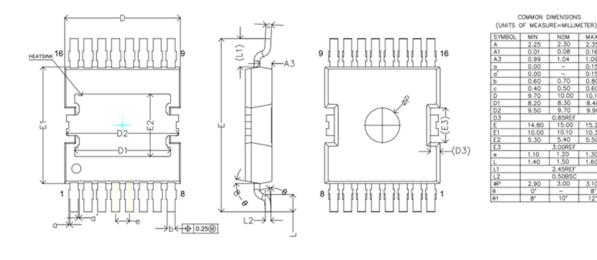

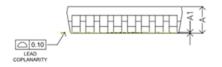

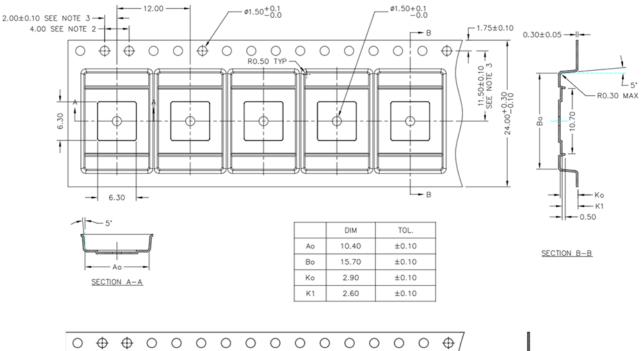

# 16. Package Outline Dimensions:

NOTES: 1.ALL DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSION.

# 17. TnR Drawing

# 18. Ordering Information

| Part Number | Qualification | Package        | MSL Rating | TnR Dia. and Qty            |

|-------------|---------------|----------------|------------|-----------------------------|

| NV6427      |               | TOLT-16L       | 2          | Standard (13" dia) Qty1,500 |

| NV6427-RA   | JEDEC         | Top-cooled SMD | 3          | Mini-Reel (7" dia) Qty450   |

# 19. Revision History

| Date                        | Status   | Notes                                                                          |

|-----------------------------|----------|--------------------------------------------------------------------------------|

| Apr 2 <sup>nd</sup> , 2024  | Revision | Updated Electrical Characteristics and Curves data                             |

| Oct 11 <sup>th</sup> , 2024 | Revision | Updated Electrical Characteristics and Curves data                             |

| Jan 23 <sup>rd</sup> , 2025 | Revision | Updated Inductive Switching Reference Schematic and Electrical Characteristics |

| Mar 6 <sup>th</sup> , 2025  | Final    | Updated Features section                                                       |

### **Additional Information**

EXCEPT TO THE EXTENT THAT INFORMATION IN THIS DATA SHEET IS EXPRESSLY AND SPECIFICALLY WARRANTED IN WRITING BY NAVITAS SEMICONDUCTOR ("NAVITAS"), EITHER PURSUANT TO THE TERMS AND CONDITIONS OF THE LIMITED WARRANTY CONTAINED IN <u>NAVITAS' STANDARD TERMS AND CONDITIONS OF SALE</u> OR A WRITTEN AGREEMENT SIGNED BY AN AUTHORIZED NAVITAS REPRESENTATIVE, (1) ALL INFORMATION IN THIS DATA SHEET OR OTHER DESIGN RESOURCES PROVIDED BY NAVITAS, INCLUDING WITHOUT LIMITATION RELIABILITY AND TECHNICAL DATA, REFERENCE DESIGNS, APPLICATION ADVICE OR TOOLS, AND SAFETY INFORMATION (COLLECTIVELY, "DESIGN RESOURCES"), ARE PROVIDED "AS IS" AND WITH ALL FAULTS; AND (2) NAVITAS MAKES NO WARRANTIES OR REPRESENTATIONS AS TO ANY SUCH INFORMATION OR DESIGN RESOURCES AND HEREBY DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

**CUSTOMER RESPONSIBILITIES.** This data sheet and other Design Resources provided by Navitas are intended only for technically trained and skilled developers designing with Navitas- or GeneSiC-branded products ("Products"). Performance specifications and the operating parameters of Products described herein are determined in the independent state and may not perform the same way when installed in customer products. The customer (or other user of this data sheet) is solely responsible for (a) designing, validating and testing the application, products and systems in which Products are incorporated; (b) evaluating the suitability of Products for the intended application and the completeness of the information in this data sheet with respect to such application; (c) ensuring the application meets applicable standards and any safety, security, regulatory or other requirements; (d) procuring and/or developing production firmware, if applicable; and (e) completing system qualification, compliance and safety testing, EMC testing, and any automotive, high-reliability or other system qualifications that apply.

**NON-AUTHORIZED USES OF PRODUCTS.** Except to the extent expressly provided in a writing signed by an authorized Navitas representative, Products are not designed, authorized or warranted for use in extreme or hazardous conditions; aircraft navigation, communication or control systems; aircraft power and propulsion systems; air traffic control systems; military, weapons, space-based or nuclear applications; life-support devices or systems, including but not limited to devices implanted into the human body and emergency medical equipment; or applications where product failure could lead to death, personal injury or severe property or environmental damage. The customer or other persons using Products in such applications without Navitas' agreement or acknowledgement, as set forth in a writing signed by an authorized Navitas representative, do so entirely at their own risk and agree to fully indemnify Navitas for any damages resulting from such improper use.

**CHANGES TO, AND USE OF, THIS DATA SHEET.** This data sheet and accompanying information and resources are subject to change without notice. Navitas grants you permission to use this data sheet and accompanying resources only for the development of an application that uses the Products described herein and subject to the notices and disclaimers above. Any other use, reproduction or display of this data sheet or accompanying resources and information is prohibited. No license is granted to any Navitas intellectual property right or to any third-party intellectual property right.

**TERMS AND CONDITIONS.** All purchases and sales of Products are subject to <u>Navitas' Standard Terms and Conditions of Sale</u>, including the limited warranty contained therein, unless other terms and conditions have been agreed in a writing signed by an authorized Navitas representative. This data sheet, and Navitas' provision of this data sheet or other information and resources, do not expand or otherwise alter those terms and conditions.

Navitas, GeneSiC, the Navitas and GeneSiC logos, GaNFast, GaNSafe and other Navitas marks used herein are trademarks or registered trademarks of Navitas Semiconductor Limited or its affiliates. Other trademarks used herein are the property of their respective owners.

Copyright © 2024 Navitas Semiconductor Limited and affiliates. All rights reserved.